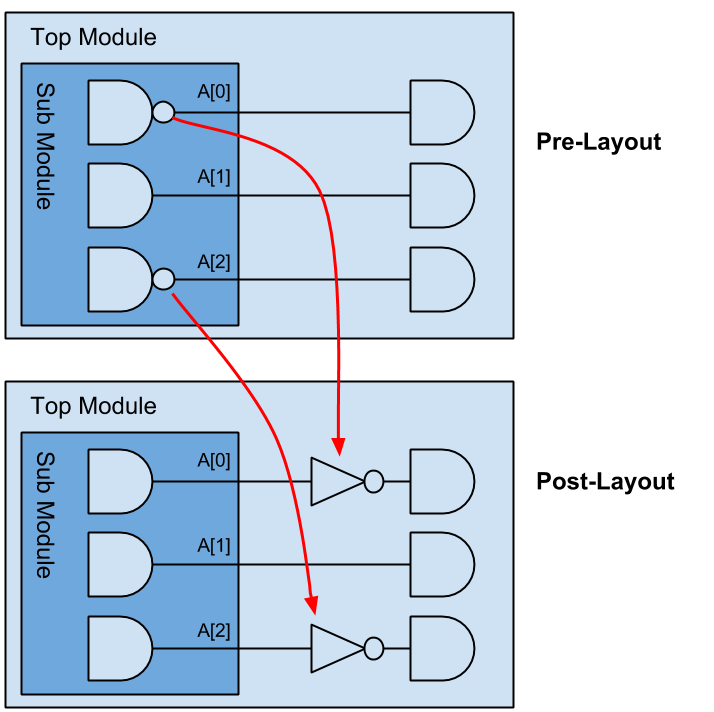

In Place & Route stage, backend tool may change a port's phase. So a bus port name is the same in post-layout netlist, but logic wise, one or more of the bus bits may have been inverted caused by inverter moved across hierarchy boundary, as shown in Figure 1. Bus port 'A' in module 'Sub Module' has bit 0 and bit 2 inverted, and the parent level module has inverters inserted in fanouts of bit 0 and bit 2. It is called boundary optimization in P&R stage.

Figure 1, Boundary Optimization in Post-Layout

However, it's annoying in gate level simulation when post-layout netlist is used. The value testbench polling on the port 'A' can be different from RTL simulation to gate level simulation. So the port phase in post-layout netlist should be checked against pre-layout netlist to adjust gate level read value.

This use case is to show how to figure out if a port has its phase changed during P&R stage.

Gates On the Fly supports Logic Equivalence Check on individual net or bus. By loading reference netlist, it's easy to find out if a net is equal, non-equal or invert to the reference net.

The reference netlist is normally pre-layout netlist which has the logic boundary preserved as RTL.

Create a GofCall script (Perl syntax) to read in both post-layout netlist and pre-layout netlist. And use 'compare' command to check the buses equivalence.

# GofCall ECO script, boundary_opti_debug.pl use strict; read_library("/proj/lib/tsmc40nm.lib"); # Read in standard library # Read in post-layout netlist which is under check read_design("-imp", "post_layout.gv"); # Read in pre-layout netlist which is for reference read_design("-ref", "pre_layout.gv"); set_top("dit_mod"); # Set the module scope compare("data_out"); # Check bus port 'data_out' phase set_top("dot_mod"); # Do the second module compare("ctrl_state"); # Check bus port 'ctrl_state' phase

Use command line 'gof -run boundary_opti_debug.pl' to execute the script.

The output message will show if any bit of the bus has been inverted, or if the bit is non-equivalent.

# Check Logic Equivalence of 'data_out' in module 'dit_mod'

u_core/u_dit_top/u_dit_mod/data_out[0] is inverted in REF and IMP

u_core/u_dit_top/u_dit_mod/data_out[1] is equal in REF and IMP

u_core/u_dit_top/u_dit_mod/data_out[2] is equal in REF and IMP

u_core/u_dit_top/u_dit_mod/data_out[3] is equal in REF and IMP

u_core/u_dit_top/u_dit_mod/data_out[4] is equal in REF and IMP

u_core/u_dit_top/u_dit_mod/data_out[5] is equal in REF and IMP

Total equal:5 inv:1 non-equal:1

# Check Logic Equivalence of 'ctrl_state' in module 'dot_mod'

u_core/u_dit_top/u_dot_mod/ctrl_state[0] is equal in REF and IMP

u_core/u_dit_top/u_dot_mod/ctrl_state[1] is equal in REF and IMP

u_core/u_dit_top/u_dot_mod/ctrl_state[2] is equal in REF and IMP

u_core/u_dit_top/u_dot_mod/ctrl_state[3] is equal in REF and IMP

Total equal:4 inv:0 non-equal:0