GOF outperforms Conformal ECO in many aspects. From 50 industry use cases we received from users, GOF beats Conformal in ECO patch size, stability and effectiveness. The 50 cases have netlist size ranging from 100K to 2.5M instance count. The ECO setups are all the same that is using a reference netlist to fix the netlist under ECO without any external help or guidance file.

Out of the 50 ECO use cases, GOF wins in 6 cases with much smaller ECO patch size. Conformal has 2 cases that achieve better patch size over GOF. Conformal seems to work hard to combine small logic gates into complicated gates in ECO results, for example, by combining four OR and AND gates into a AOI gate. So when Conformal has smaller number of ECO patch in gate count, it doesn't save actual area.

Conformal fails to get equivalent ECO result netlists in 3 cases while GOF can make all 3 cases ECO results equivalent. Conformal even hangs in one of the 3 cases. Both GOF and Conformal fail to fix one big ECO case. The rest 38 cases have similar results between GOF and Conformal.

GOF has very good control of memory usage starting from Version 7 comparing with previous versions and the above use cases all have similar memory usage between GOF and Conformal. Conformal still has speed advantage. GOF is slower by 50% in average. When netlist size is small, ~200K gate count or less, Conformal shows much faster speed. But Conformal doesn't keep the advantage when netlist gate count is above 500K.

Conformal ECO has at least four performance bugs. First, Conformal has a bug in handling complicated combinational logic ECO. Secondly, Conformal has trouble to mapping replicated flops. Thirdly, Conformal doesn't do good job when ECO fix involving DFT scan chain. And one more bug is in Design Ware handling that Conformal adds too many redundant ECO gates when Design Ware instance names change in synthesis.

A combinational signal in RTL is mostly optimized away after synthesis. It brings difficulty in pinpointing the ECO location if the ECO is done manually. So Logic ECO tool is used to locate the ECO point by comprehensive algorithms. And the accuracy of the location and size of ECO patch is to measure the quality of the ECO tool.

Conformal has a bug in Complicated Combinational Logic ECO. In some ECO case, it can't figure out the exact ECO location and the ECO patch is much larger than necessary. Or in other ECO cases, conformal has no problem in pinpointing the ECO location, but it produces redundant logic in fixing the ECO spot.

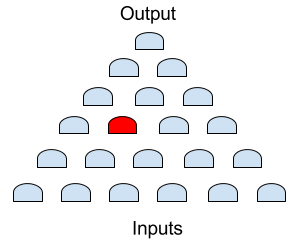

For example, Figure 1 shows a single combinational signal ECO case. One signal in the middle of a combination logic cone has been modified. The ECO tool should find the exact location in the Implementation Netlist and replace the original logic by the new logic in the Reference Netlist.

Figure 1: Single error, red spot is the failing logic

As shown in the following Verilog pseudo-code, one RTL design has one if-condition changed in a big state machine. A new combinational signal is added into the if-condition.

always @(*) begin

case(current_state[7:0])

IDLE: begin

if(comb_sig0) next_state = START;

else next_state = IDLE;

end

START: begin

if(comb_sig1&comb_sig2|!comb_sig3) next_state = STATE1;

else if(comb_sig4&comb_sig5&!comb_sig6|eco_comb_sig) next_state = STATE2;

else if(comb_sig7|comb_sig8&!comb_sig9) next_state = STATE3;

...

end

assign eco_comb_sig = pcie_mode && beacon_status; // New combinational signal

Very likely, Conformal ECO fails to find the exact location to fix the combination signal change. Or it finds the location, but it uses more than enough gates to fix the logic and the surrounding logic is affected unnecessarily. Conformal has the issue in at least three cases out of the 50 cases.

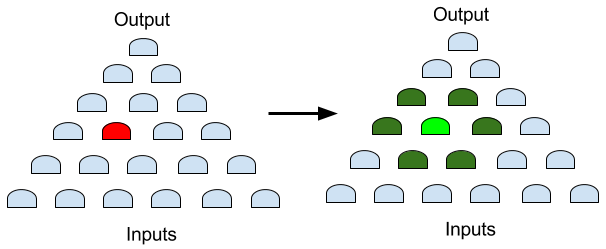

Figure 2: Conformal ECO result, dark green spots are the redundant fixes

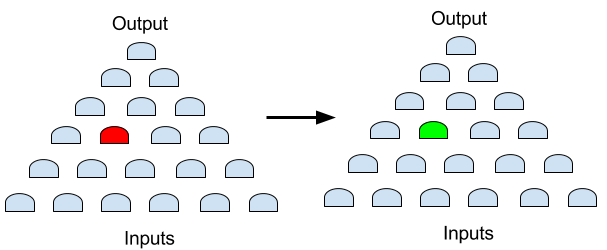

GOF is able to pinpoint the exact ECO location. And the ECO fix is exactly on the red spot. So that the final ECO patch is the most optimal.

Figure 3: GOF result, only fix the red spot

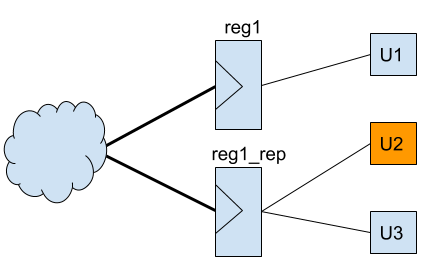

Replicated flops are two or more flops have the same function. The data pins and set/reset pins of these flops have the same functions. The replicated flops can be in the original RTL file or they can be generated by synthesis tool during special setting run, for example, physical optimization enabled to enhancing timing and area.

These flops should be mapped as the same key points by the ECO tool. But Conformal ECO seems having trouble in mapping these replicated flops in some cases.

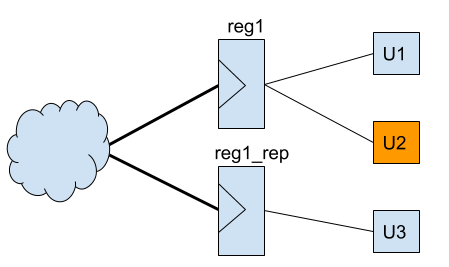

For example, as shown in Figure 4, a flop named reg1 can have an equivalent replicated flop reg1_rep after synthesis. Sometimes, Conformal doesn't treat them as equivalent key points.

Figure 4: Flop replicated after synthesis

During ECO, RTL is modified and re-synthesized. The flop reg1 and its replicated flop reg1_rep have one fanout 'U2' swapped, as shown in Figure 5, and they are actually logically equivalent.

Figure 5: Flop reg1 and reg1_rep have fanout swapped

Since Conformal ECO treats reg1 and reg1_rep as different functional key points, it results in a redundant ECO fix logic.

One simplest use case to fail Conformal is like this:

//IMP Implementation Netlist module top(a,b,c,d,clk,out); input a,b,c,d,clk; output out; AND2X1 u0(.A(a),.B(b),.Z(ab)); DFFQX1 b_flop(.D(ab),.CK(clk),.Q(out0)); XOR1X1 u1(.A(out0),.B(d),.Z(out)); DFFQX1 a_flop(.D(c),.CK(clk),.Q(out_floating)); endmodule

//REF Reference Netlist

module top(a,b,c,d,clk,out);

input a,b,c,d,clk;

output out;

AND2X1 u0(.A(a),.B(b),.Z(ab));

DFFQX1 a_flop(.D(ab),.CK(clk),.Q(out0));

XOR2X1 u1(.A(out0),.B(d),.Z(out));

endmodule

The two netlists are equivalent, but the default key point mapping of Conformal screws up the result. GOF can recognize a_flop as floating flop in the Implementation Netlist and successfully map b_flop in the Implementation Netlist to a_flop in the Reference Netlist. It's problematic for Conformal, since such mapping is pretty common in ECOs.

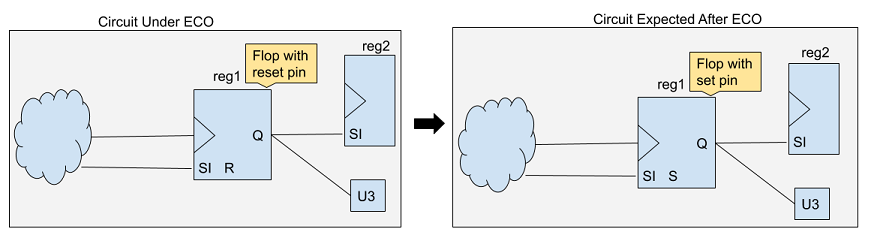

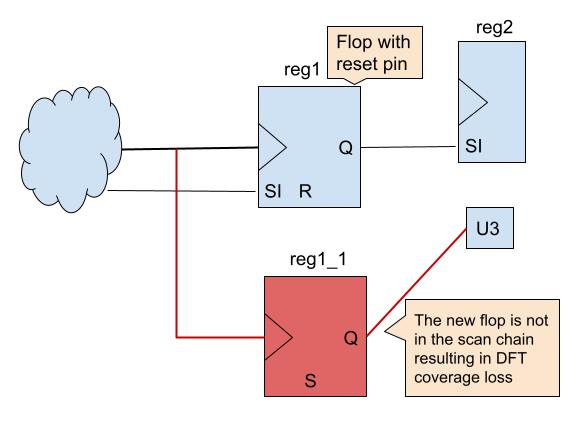

During functional ECO, DFT related pins are configured to set DFT circuit in ignore mode. However, in order to achieve the best functional ECO result, DFT logic should be treated as 'Dont Care' instead of 'Dont Touch'. There is difference between 'Dont Care' and 'Dont Touch'. 'Dont Care' mode can tune up the DFT logic and 'Dont Touch' mode forbids any logic change in the DFT logic.

For example, Figure 6 shows an ECO to change the flop reg1 from reset type flop to set type flop. The best solution is to convert the flop reg1 to a set type flop which means the DFT logic is treated as 'Dont Care', since the scan chain fanout reg2 is now driven by different type of flop.

Figure 6: Reset flop changed to set flop in ECO

Conformal treats DFT logic as absolutely 'Dont Touch'. So after ECO, a new set type flop reg1_1 is created to drive the original functional circuit and the old flop reg1 still drives the scan chain fanout reg2. It is not optimal solution and also it causes a new problem. Conformal LEC treats the new flop reg1_1 as not mapped key point. Ant it results in lots of non-equivalent points in equivalence report after ECO.

Figure 7: Conformal uses inefficient solution to add new set type flop in ECO

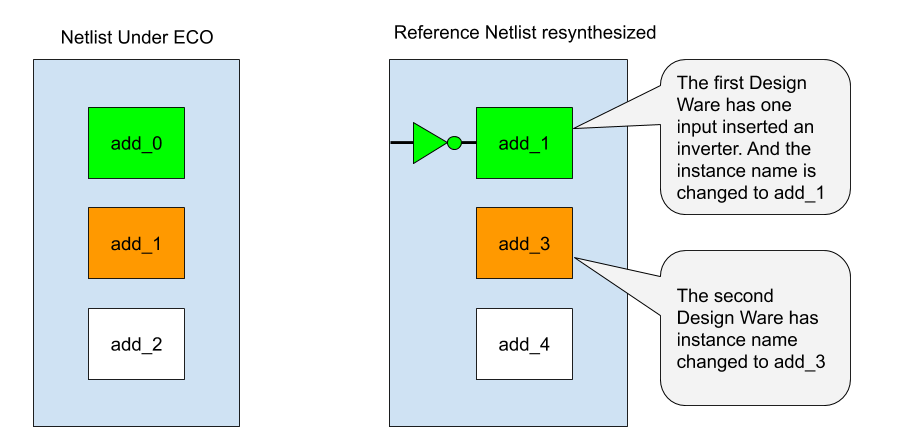

Synopsys DC synthesis writes out Design Ware as hierarchical modules by default. The instance names of Design Wares assigned by DC can be different in a second run when there is RTL changes. For example, a design has three adder arithmetic elements, and they are assigned instance names, add_0, add_1 and add_2 respectively. After RTL changes, a second synthesis has the three arithmetic elements assigned instance names as add_1, add_3 and add_4. That means the first adder takes the third adder's instance name in the new synthesis.

The ECO change is on the first adder, add_0 in the Implementation Netlist and it has name changed to add_1 in the Reference Netlist during synthesis.

Figure 8: Design Ware instance names changed during synthesis

The optimal ECO result should be one inverter inserted in add_0's input. However, Conformal has very poor performance in dealing with this ECO. All gates in the new add_3 Design Ware are flatten and added as new ECO gates. Several new full adder cells are added due to the inverter gate.

While GOF redoes the mapping of the Design Ware instances if the two netlists don't have full instance mapping of the combinational modules include Design Wares. So the final result of GOF is one inverter inserted in the ECO which is optimal.

These bugs in Conformal ECO hurt its performance in many ECO cases. GOF beats Conformal in these ECO cases in patch size and efficiency. Overall, GOF outperforms Conformal ECO by achieving smaller patch size, more stable in ECO runs and more likely to get equivalent results.