Performing a complete top-level netlist synthesis can be time-consuming. GOF provides APIs enabling the integration of newly synthesized sub-modules into the original pre-layout netlist, along with updates to the top-level SVF file. This incremental approach allows the generation of the large top-level netlist and the top-level SVF file, resulting in significant time and effort savings. At the RTL level, designers identify modified RTL modules during ECO and synthesize them to create netlist and SVF files. Some altered RTL modules, particularly sub-parent modules with only sub-module instantiations, may not require synthesis.

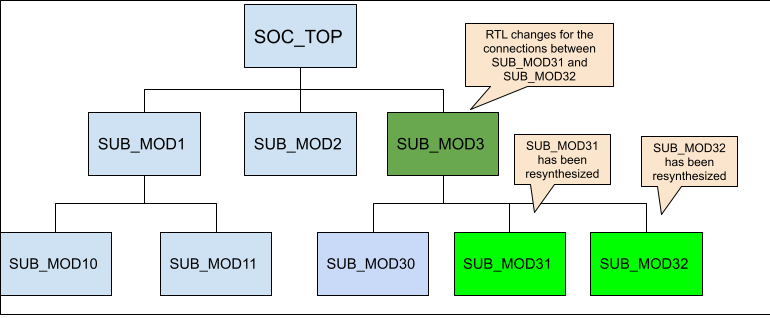

In Figure 1, only two sub-modules, SUB_MOD31 and SUB_MOD32, require re-synthesis in the extensive SOC_TOP design. Their parent module has only experienced connection changes and remains in netlist format, eliminating the need for synthesis. The example below illustrates how to process these files and generate a new SOC_TOP level netlist and SVF file.

Figure 1: Sub-modules to be synthesized

Step 1: Add missing DFT ports

The newly synthesized sub-modules may lack certain ports present in the original netlist. Notably, ports essential for scan in and scan out are typically added by the DFT tool. Since the DFT process is not applied to the new synthesized sub-modules, it's necessary to incorporate these ports as dummy ones within the modules to avoid syntax errors.

The procedure for incorporating DFT ports into the newly synthesized modules is as follows:

use strict; read_library("tsmc.lib"); read_design("-ref", "SOC_TOP.pre_layout.gv");# Read in the original pre_layout netlist read_design("-imp", "SUB_MOD31.new_syn.gv");# Read in new synthesized netlist set_tree("ref"); set_top("SUB_MOD31_1"); # The old pre-layout netlist may have this module with prefix or suffix added in uniquify my @ref_port_ins = get_ports("-input"); my @ref_port_outs = get_ports("-output"); set_tree("imp"); set_top("SUB_MOD31"); my @imp_port_ins = get_ports("-input"); my @imp_port_outs = get_ports("-output"); my $cnt = 0; foreach my $port (@ref_port_ins){ if(!grep($port eq $_, @imp_port_ins)){ # The input port is not in the new synthesized module new_port($port, "-input"); gprint("$cnt: Warning input $port is not in the new synthesized sub-module\n"); $cnt++; } } foreach my $port (@ref_port_outs){ if(!grep($port eq $_, @imp_port_outs)){ # The output port is not in the new synthesized module new_port($port, "-output"); gprint("$cnt: Warning output $port is not in the new synthesized sub-module\n"); $cnt++; } } write_verilog("SUB_MOD31.dft_ports_added.gv"); exit;

The identical process should be executed on SUB_MOD32 to include the necessary DFT-related ports.

Step 2: Replace sub-modules netlist and SVF

During this step, the DFT ports added netlist and SVF files of the synthesized sub-modules are read to substitute the original pre-layout netlist and SVF files.

The procedure for replacing netlist and SVF:

read_library("tsmc.lib"); read_svf("-imp", "SOC_TOP.pre_layout.svf"); read_design("-imp", "SOC_TOP.pre_layout.gv"); read_sub_module_svf("SUB_MOD31.svf.txt", "-module", "SUB_MOD31_1", "-syn_module", "SUB_MOD31"); read_sub_module_svf("SUB_MOD32.svf.txt", "-module", "SUB_MOD32_1", "-syn_module", "SUB_MOD32"); read_sub_module_netlist("SUB_MOD31.dft_ports_added.gv", "-module", "SUB_MOD31_1", "-syn_module", "SUB_MOD31"); read_sub_module_netlist("SUB_MOD32.dft_ports_added.gv", "-module", "SUB_MOD32_1", "-syn_module", "SUB_MOD32"); read_sub_module_netlist("SUB_MOD3.new.v", "-module", "SUB_MOD3_1", "-syn_module", "SUB_MOD3", "-sub_only"); # Need sub_only option replace_sub_module_netlist("SOC_TOP.new_reference.gv"); # Replace netlist should be run first replace_sub_module_svf("SOC_TOP.new_reference.svf"); # Then replace SVF

After the generation of both the top-level netlist and SVF files, they can be incorporated into the complete top-level automatic ECO process.