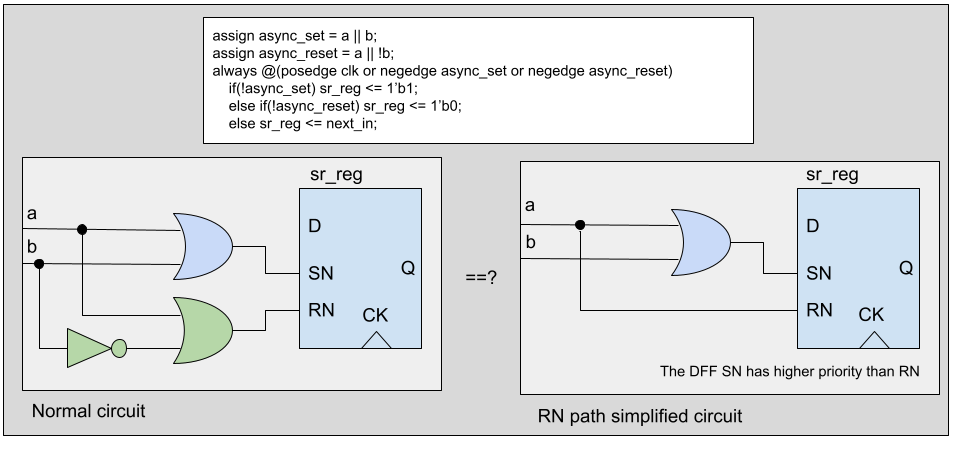

An effective ECO tool should not only address functional logic issues but also consider aspects such as DFT, timing, and simulation. For instance, as illustrated in Figure 1, the RTL is typically synthesized into a set-reset D Flip-Flop (DFF) in the left-side circuit. However, the DFF's higher priority in set pin SN, confirmed by the clear_preset_var1 variable in the liberty file or the library simulation model, may lead some synthesis or other tools to simplify the circuit on the right side. Despite these modifications, both circuits remain equivalent in logic equivalence checking.

Figure 1: Set reset priority in DFF

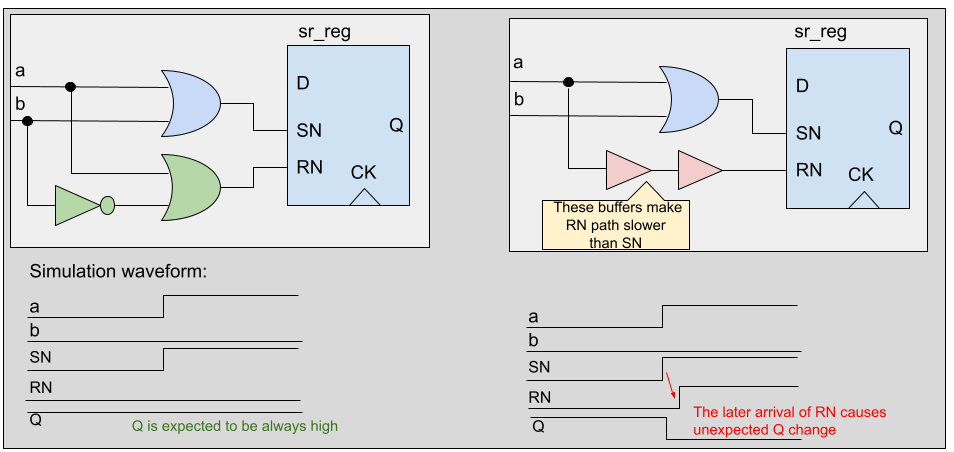

Nonetheless, a race condition arises in the set and reset paths in the simplified circuit on the right. If the RN path experiences delays due to the insertion of multiple buffers, surpassing the delay in the SN path, a simulation may reveal the occurrence of glitches.

Figure 2: Simulation issue in set reset DFF

While other LEC or ECO tools solely affirm the equivalence of two circuits, they lack a mechanism to pinpoint potential simulation issues resulting from circuit simplification. If such problems are only identified during simulation, it can significantly impact project schedules, requiring more time for troubleshooting. GOF ECO not only verifies the equivalence of the two circuits but also introduces an option to detect simplified circuits. This feature enables designers to identify issues at an earlier stage. By generating a reliable reference netlist with the standard set/reset circuit, GOF ECO performs an ECO on the Implementation Netlist, rectifying any set/reset circuit modifications.

The following example is to disable set/reset pin priority by force:

read_library("tsmc.lib");# Read in standard library read_design("-ref", "good_netlist_with_sn_rn.v"); # Reference netlist read_design("-imp", "netlist_with_sn_rn_issue.v"); # netlist under ECO set_sn_vs_rn(0); # Force to disable set/reset pin priority fix_design();