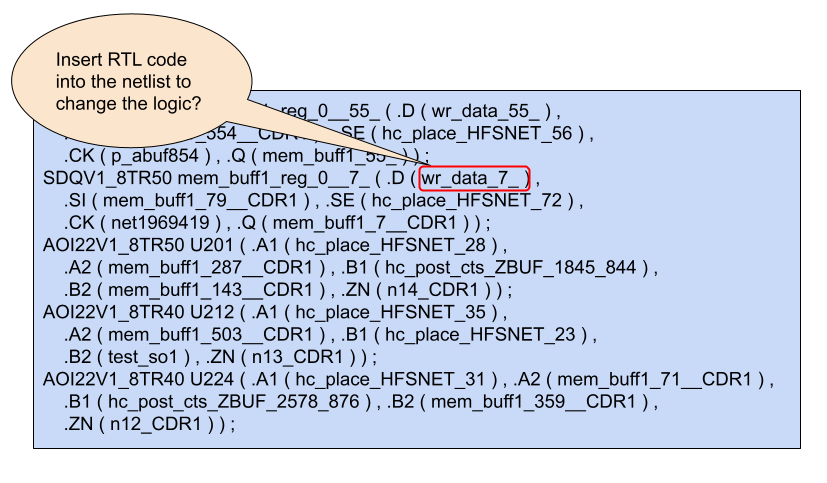

In today's landscape, IC design has become increasingly complex, often resulting in lengthy synthesis processes that can take several days to complete. Automatic functional netlist ECO requires synthesizing the whole updated RTL into a reference netlist. However, even for small and straightforward RTL modifications, this process can be time-consuming and impact the overall design schedule. An alternative approach is to directly insert RTL code into the netlist for netlist ECO. Is this approach feasible?

Figure 1: Insert RTL to netlist

When dealing with RTL changes that are relatively simple and involve only a single logic functional modification, the traditional approach of synthesizing the code snippet in a new module and then inserting it back into the netlist can indeed present challenges. One particular challenge is the resolution of net name conflicts that may arise during this process.

GOF ECO offers a viable solution for directly inserting an RTL patch into the netlist, facilitating incremental synthesis. By employing this approach, the ECO tool can generate an optimized netlist where the RTL patch is converted into a logic patch, while striving to preserve the original netlist to the greatest extent possible.

This methodology ensures that the RTL modifications are seamlessly integrated into the existing netlist without the need for complete resynthesis. Instead, only the affected portions of the design are synthesized incrementally, resulting in significant time savings compared to a full synthesis process.

During the incremental synthesis, the ECO tool takes into account the RTL patch and makes targeted modifications to the affected logic without extensively altering the rest of the netlist. This optimization process aims to minimize disruptions to the original design and maintain its functionality as closely as possible.

Upon completion of the synthesis, the ECO tool generates a new netlist that reflects the integrated changes. The RTL code is transformed into a logic patch representation within the netlist. This allows for a streamlined integration process while ensuring the modified design adheres to the desired specifications.

By leveraging the incremental RTL patch methodology, design teams can effectively manage functional changes without compromising the overall design schedule. This approach provides an optimal solution that combines the advantages of direct RTL patch insertion with incremental synthesis, enabling efficient netlist modifications while preserving the integrity of the original design as much as possible.

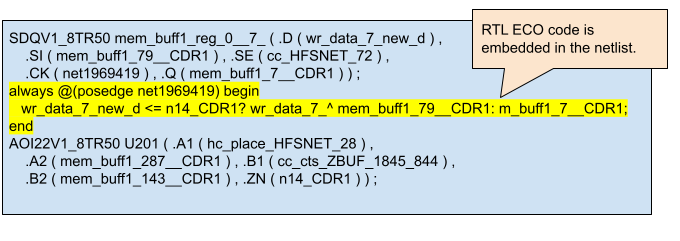

In Figure 2, the RTL always statement is directly inserted into the netlist. When utilizing GOF ECO, the netlist containing the inserted RTL patch is read, and the ECO tool initiates an incremental synthesis process. This incremental synthesis incorporates the necessary changes specified by the RTL patch. As a result, the final ECO netlist incorporates the required logic patch, reflecting the modified design accurately.

Figure 2: RTL patch embedded

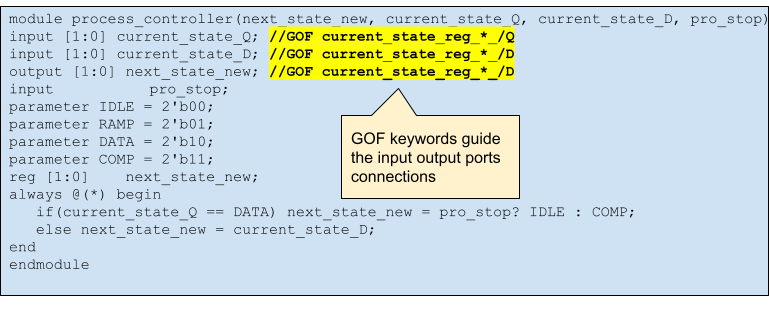

In addition to direct RTL code insertion, GOF ECO offers more advanced and intricate methods for handling RTL patches. For example, as depicted in Figure 3, the RTL code patch can be stored in a separate patch file. This patch file serves the purpose of updating and replacing a multi-bit state machine within the netlist.

With GOF ECO, it is capable of efficiently reading and processing the patch file. It then proceeds to perform the necessary modifications required to update and replace the targeted multi-bit state machine within the netlist. By leveraging incremental synthesis techniques, only the relevant sections of the design undergo synthesis, minimizing any potential impact on the remainder of the netlist.

Figure 3: RTL patch replaces state machine

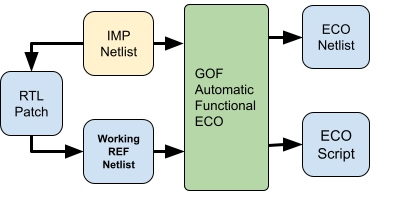

The GOF ECO RTL patch method leverages keywords and incremental synthesis to facilitate complex ECO processes while maintaining a fast turnaround time. This methodology involves applying the RTL patch to the Reference Netlist and utilizing the automatic ECO feature to fix the Implementation Netlist. By doing so, the ECO patch can be fully optimized for optimal performance.

Using key words and incremental synthesis, GOF ECO streamlines the ECO process by efficiently identifying and implementing the necessary modifications. The RTL patch is initially applied to the Reference Netlist, which serves as a reference for the desired changes. The automatic ECO feature then enables the use of the Reference Netlist to rectify and refine the Implementation Netlist.

Figure 4: RTL patch optimization flow