Swapping resettable settable flops is a common practice during functional netlist ECO. This is particularly evident in RTL code, where changes in the default values within the reset statement can result in resettable/settable type flop swapping in the synthesis netlist. An ECO that is DFT and timing friendly should strive to make the minimum number of changes to the circuit.

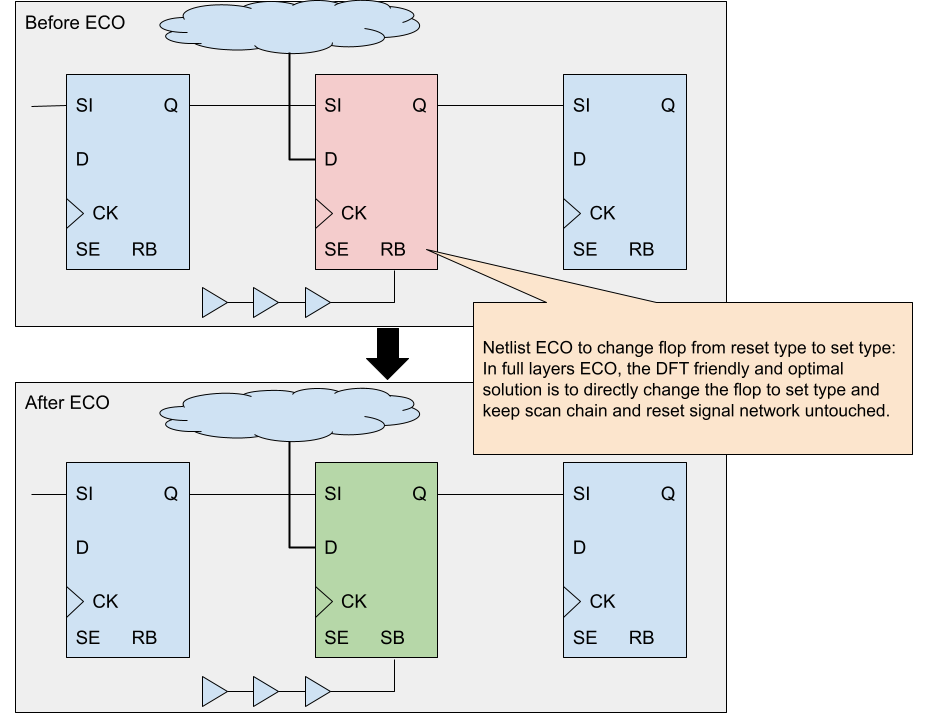

As depicted in Figure 1, suppose a resettable type flop needs to be swapped with a settable type flop. In that case, the optimal ECO solution is to replace the flop directly with a settable type flop while keeping the scan chain and reset signal network untouched. This approach ensures that the ECO is DFT-friendly and timing-friendly, and this is precisely how GOF ECO operates.

Figure 1: Reset set flop swap, keep DFT and reset network untouched

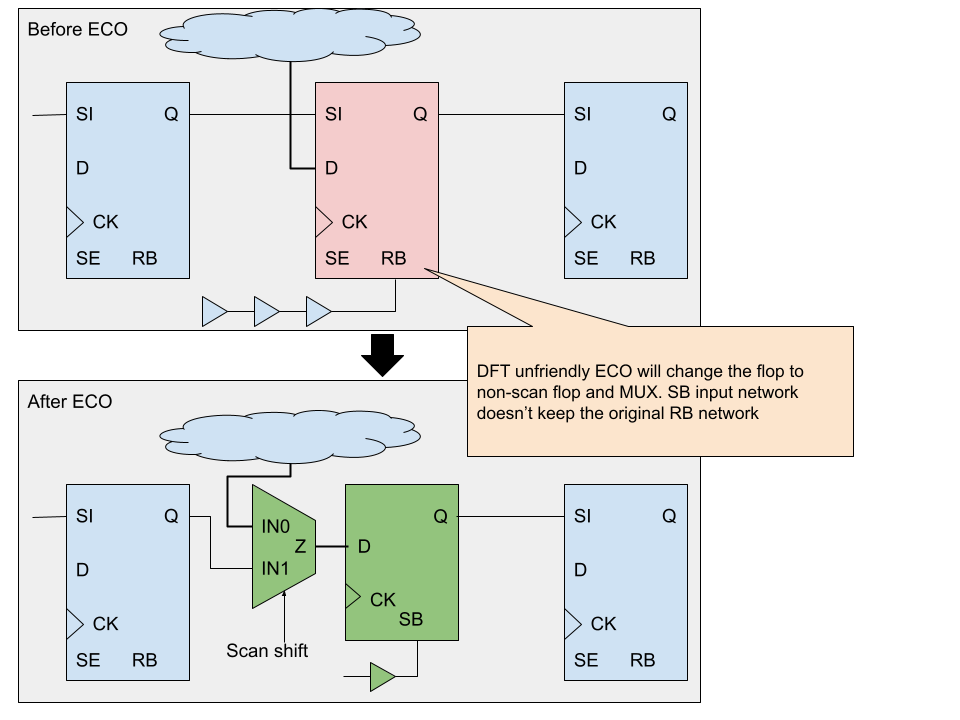

An ECO that is DFT-unfriendly replaces the original scan flop with a non-scan flop with settable type. Additionally, an extra MUX is added to choose between the scan shift mode or functional mode. As illustrated in Figure 2, this approach is DFT-unfriendly, even though the DFT may still function. Moreover, the reset signal network is modified to use a different signal. This behavior is typical of Conformal ECO.

It is essential to note that such changes can have negative impacts on the design's testability and timing performance. Therefore, designers must adopt DFT and timing-friendly ECO solutions to ensure that the changes made do not adversely affect the overall design's functionality and performance.

Figure 2: DFT unfriendly solution

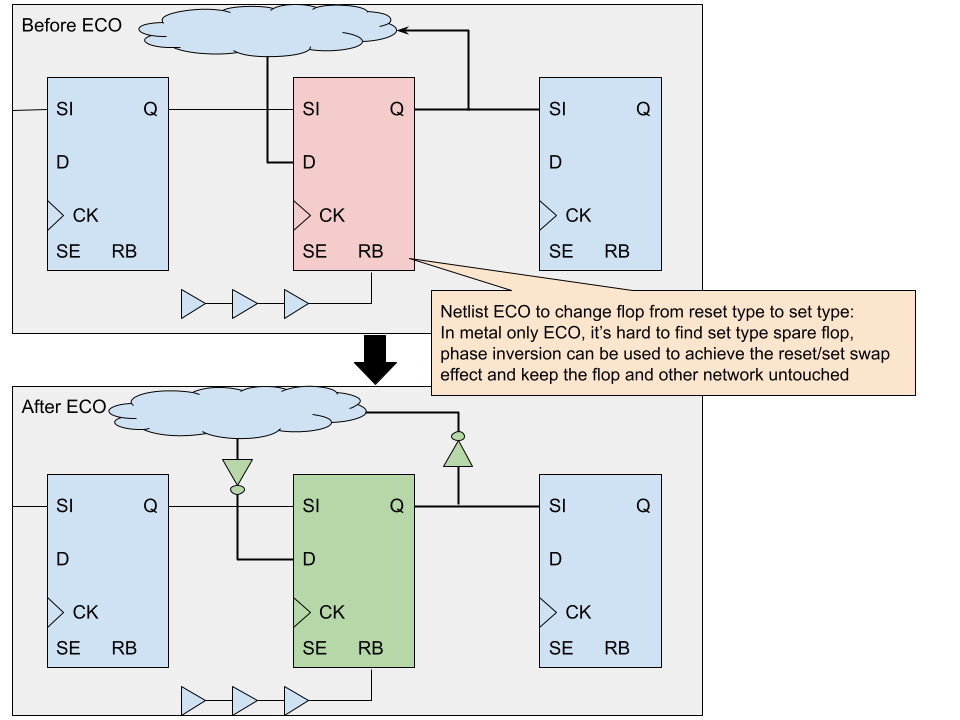

Metal Only ECO can present challenges in finding a nearby corresponding spare flop for resettable/settable swapping. In such cases, the phase inversion method can be used to achieve the same effect. By inserting inverts in the D input and Q output driving functional fanout, as illustrated in Figure 3, the ECO can be accomplished at minimal cost in Metal Only ECO.

However, it is crucial to handle the phase inversion logic correctly during logic equivalence checking. A special command, set_mapping_method, is required to ensure that the phase-inverted flip-flop is mapped correctly. For more information on flip-flop phase inversion, please refer to the relevant documentation. See Flip-flop Phase Inverted for more detail.

Figure 3: In metal only ECO, use phase inversion to achieve resettable settable swapping effect

In conclusion, different approaches are required to ensure optimal performance during pre-mask and post-mask design stages. While changing the flop type is relatively simple during the pre-mask stage, it can be a challenging task during the post-mask stage, as locating a corresponding spare flop can be difficult. In such cases, techniques like phase inversion or adding inverters to the input and output pins of the flop can be used.

Furthermore, it is crucial to consider the impact of design changes on factors such as testability and timing performance. Hence, designers should adopt DFT and timing-friendly ECO solutions to ensure that the changes made do not adversely affect the overall design's functionality and performance.

By carefully selecting and implementing the appropriate ECO techniques, designers can achieve optimal performance and ensure that their designs meet the desired specifications.