The synthesis of a large SOC design is known for its time-intensive nature, often taking several days to complete. In cases where a functional ECO is necessary, particularly concerning a specific sub-module, the design team opts to confine the ECO to that particular sub-module instead of initiating synthesis for the entire design. Following this, the ECO results for the sub-module are retargeted onto the full top-level netlist. This strategy significantly accelerates the turnaround time and ensures the project schedule remains on track.

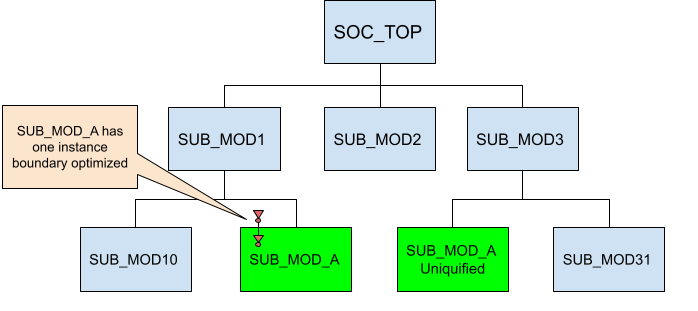

However, the team must factor in the boundary optimization of the sub-modules during backend processing. A given sub-module may have undergone unique transformations, resulting in the creation of multiple distinct physical modules with diverse backend optimizations. Illustrated in Figure 1, an instance of SUB_MOD_A may exemplify a backend modification, such as a port inversion.

Consequently, the automatic ECO process must be designed to account for these variations in backend processing, ensuring a comprehensive and accurate adaptation to the specific characteristics of each sub-module.

Figure 1: Instances of one sub-module have different boundary optimization

The boundary optimization challenge in GOF is addressed by incorporating the original pre-layout netlist. This is possible because the pre-layout netlist should mirror the state of the netlist before any ECO is implemented, with the boundary remaining unchanged prior to the placement and routing phase.

To extract the boundary optimization of sub-modules during ECO, a comparison is made between the pre-layout netlist and the netlist under ECO. As the automatic ECO is applied to individual sub-modules, the relevant boundary optimization information is retroactively annotated. This ensures the precision of the ECO and establishes equivalence when comparing top-level designs.

The loading of the pre-layout netlist is facilitated by using the "-ori_syn" option in the "read_design" command.

ECO retargeting script:

read_design('-ref', "new_sub_mode_a.gv"); # New synthesized sub-module-A read_design('-imp', "post_layout.gv"); # Full post layout netlist read_design('-ori_syn', "pre_layout.gv"); # Full prelayout, equal to post_layout.gv # Apply ECO to the first instance set_top_ref("SUB_MOD_A"); # Must set REF scope set_top("SUB_MOD_A_0"); # Uniquified name for the first instance fix_design(); # Apply ECO to the second instance set_top_ref("SUB_MOD_A"); # Must set REF scope set_top("SUB_MOD_A_1"); # Uniquified name for the second instance fix_design(); set_top("SOC_TOP"); report_eco(); write_verilog("post_layout.eco.gv"); # Full post layout netlist after ECO

This entire retargeting procedure is notably more time-efficient compared to performing a full netlist ECO. With the boundary information being meticulously addressed, the resulting ECO is highly accurate.

Check GOF Manual for more detail